# MITRE

# The EMB3D<sup>™</sup> Threat Model for Embedded Devices

The views, opinions, and/or findings contained in this report are those of The MITRE Corporation and should not be construed as an official government position, policy, or decision, unless designated by other documentation.

©2024 The MITRE Corporation. All rights reserved. Approved for public release; Distribution unlimited. Public release case number: 24-00165-2

McLean, VA

Adam Hahn<sup>1</sup> Jack Cyprus<sup>1</sup> Dave Keppler<sup>1</sup> Marie Collins<sup>1</sup> Chris Harvey<sup>1</sup> Niyo Little Thunder Pearson Wyatt Ford<sup>2</sup> Ang Cui<sup>2</sup> Michael Locasto<sup>3</sup>

May 2024

©2024 The MITRE Corporation.

<sup>&</sup>lt;sup>1</sup> The MITRE Corporation, <sup>2</sup> Red Balloon Security, <sup>3</sup> Narf Industries

## **Table of Contents**

| 1 | Intr  | oduction                                                                                                 | .1  |

|---|-------|----------------------------------------------------------------------------------------------------------|-----|

| 2 | EM    | B3D <sup>тм</sup> Overview                                                                               | . 2 |

| 3 | EM    | B3D™ Structure                                                                                           | . 3 |

|   | 3.1   | Device Properties                                                                                        | . 3 |

|   | 3.2   | Threat Properties                                                                                        | . 4 |

|   | 3.3   | Mitigations                                                                                              | . 5 |

| 4 | Use   | rs and Workflow                                                                                          | . 6 |

|   | 4.1   | Workflow                                                                                                 | . 6 |

|   | 4.2   | EMB3D <sup>TM</sup> Use Cases for Vendors, Asset Owners, Security Researchers, and Testing Organizations | . 8 |

|   | 4.2.  | 1 User 1: Vendor Product Team                                                                            | . 8 |

|   | 4.2.  | 2 User 2: Asset Owner Security Architect                                                                 | . 8 |

|   | 4.2.  | 3 User 3: Security Researcher/Testing Organization                                                       | . 9 |

| 5 | Con   | clusion                                                                                                  | . 9 |

| A | ppend | ix A Terminology, Challenges, Scope, and Related Efforts                                                 | 10  |

|   | A.1   | Terminology                                                                                              | 10  |

|   | A.2   | Threat Maturity                                                                                          | 11  |

|   | A.3   | Key Challenges                                                                                           | 12  |

|   | A.4   | Scoping                                                                                                  | 13  |

|   | A.5   | Related Work                                                                                             | 14  |

## **1** Introduction

The security of our Nation's critical infrastructure depends on embedded devices that frequently lack adequate security controls or have not undergone sufficient testing for vulnerabilities. The prevalence of these issues is evident through the CISA ICS Advisories,<sup>1</sup> which to date have released 2,459 alerts for ICS devices and software, of which 1,243 have been given a Common Vulnerability Scoring System (CVSS) severity of at least Medium.<sup>2</sup> Further, initiatives such as the White House Industrial Control System Cybersecurity (ICS) memorandum and CISAs Secure-by-Design and -Default focus<sup>3,4</sup> identify the need to improve the security critical infrastructure and associated devices. Despite these efforts, there remains an inconsistent understanding about what threats are posed to embedded devices and what security mechanisms or capabilities mitigate them.

This document introduces the EMB3D<sup>TM</sup> threat model for critical infrastructure embedded devices. Critical infrastructure embedded devices include a broad set of unique technologies used in, but not limited to, industries such as oil, natural gas, water/wastewater management, automotive, medical, satellite, autonomous, and UAS, along with dependencies on more diverse technologies used across general computing platforms/environments. The threat model is intended to be used by vendors, asset owners/operators, test organizations, and security researchers as a resource to improve the overall security of embedded devices' hardware and software. The objective of this threat model is to provide a single repository of information defining known threats to embedded devices, which align to the unique device features/properties that enable specific threat actions. By mapping the threats to the associated device features/properties, the threat model allows the user to easily enumerate threat exposure based on the known device features. Vendors, asset owners/operators, and security researchers will then be able to identify relevant threats to devices more consistently and comprehensively and ensure those devices include the necessary mitigations to protect them from those threats. In this way, the threat model can also serve as a uniform method for organizations to track and communicate threats and associated security mechanisms in a device. It also provides a common language to communicate security requirements and protections, helps asset owners better evaluate the security claims of a device, guide evidence-based testing, and inform acquisition decisions for a device.

EMB3D<sup>TM</sup> should be considered a living framework, where new threats and mitigations are added and updated over time as threat actors and security researchers discover new categories of vulnerabilities, threats, and security defenses. Further, EMB3D<sup>TM</sup> is intended to be a public community resource, where all information is openly available, and the security community can submit additions and revisions.

#### ©2024 The MITRE Corporation.

<sup>&</sup>lt;sup>1</sup> Cybersecurity Alerts & Advisories | CISA URL: https://www.cisa.gov/news-events/cybersecurity-advisories

<sup>&</sup>lt;sup>2</sup> ICS Advisory Project. URL: https://www.icsadvisoryproject.com

<sup>&</sup>lt;sup>3</sup> National Security Memorandum on Improving Cybersecurity for Critical Infrastructure Control Systems. The White House. July 28, 2021. URL:https://www.whitehouse.gov/briefing-room/statements-releases/2021/07/28/national-securitymemorandum-on-improving-cybersecurity-for-critical-infrastructure-control-systems/

<sup>&</sup>lt;sup>4</sup> Shifting the Balance of Cybersecurity Risk: Principles and Approaches for Security-by-Design and -Default. April 13, 2023. URL: https://www.cisa.gov/sites/default/files/2023-06/principles\_approaches\_for\_security-by-design-default\_508c.pdf

This paper presents the EMB3D<sup>™</sup> threat model structure, content, and use cases associated with expected users. Additional discussion on scope, terminology, challenges, related efforts, terminology can be found in Appendix A. Mitigations will be in the next release of EMB3D, summer of 2024.

## 2 EMB3D<sup>™</sup> Overview

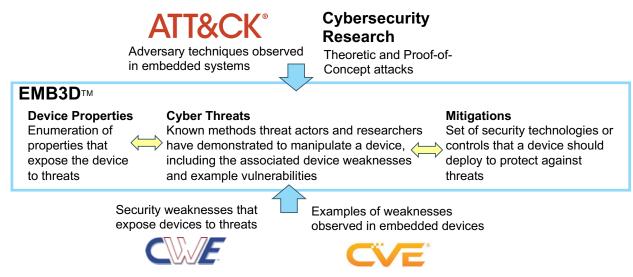

Figure 1 provides an overview of EMB3D<sup>TM</sup> and its alignment with other key security frameworks and knowledge bases. The threats defined within EMB3D<sup>TM</sup> are based on observation of use by threat actors, proof-of-concept and theoretical/conceptual security research publications, and device vulnerability and weakness reports. Mitigation requirements are defined for each threat and are focused on technical mechanisms that device vendors should implement to protect against the threats. The goal is to build in security vice the common practice of pushing responsibility for mitigations to the asset owner, which may lack the technical knowledge or financial capacity to address these issues.

A key contribution of EMB3D<sup>TM</sup> is the integration and cultivation of information on threats to embedded devices across various diverse sources. It integrates information about known adversary behaviors with references to MITRE ATT&CK<sup>®5</sup> techniques. In addition to the integration of information on known adversary behaviors, it also provides references to a wide range of theoretic and proof-of-concept vulnerability research efforts that have been demonstrated by security researchers and are documented through various security conferences, papers, blogs, and other sources. Each threat defined within EMB3D<sup>TM</sup> includes both a Threat Evidence reference and a Threat Maturity categorization:

• Threat Evidence is a reference to a reputable report describing the threat and documenting its feasibility; this can include a reference to ATT&CK techniques, or other

<sup>&</sup>lt;sup>5</sup> MITRE ATT&CK: URL: https://attack.mitre.org

documented reports or research papers/presentations. This provides the users with an easy and direct way to understand and access a continually evolving set of information and research about device threats.

• Threat Maturity categorizes how mature that threat is based on whether it (i) has been observed in the wild targeting an embedded device, (ii) is associated with a known weakness (e.g., CWE) that has been exploited, (iii) has a proof-of-concept exploit, or (iv) has a purely theoretic demonstration or description. Threat maturity is a continually evolving property. Many threats continue to mature over time, especially as security researchers make new discoveries and as more threats are seen in real environments. Therefore, the threat maturity field is intended to evolve as new threat evidence is identified.

The threat information is also mapped to a specific CWE, which defines the specific weakness in the device that enables that threat. It also provides references to CVEs, specifically those defined within CISA ICS Advisories,<sup>6</sup> as examples of those weaknesses within actual ICS devices and software platforms. This information is intended to further provide credibility about device weaknesses that need to be mitigated to protect against each threat.

## 3 EMB3D<sup>™</sup> Structure

The content of EMB3D<sup>TM</sup> is structured into three main categories: (i) device properties, (ii) threat properties, and (iii) mitigations. Information on each of these categories is provided below.

## 3.1 Device Properties

The device properties enumerate and describe various hardware and software components and capabilities of a device. These range from physical hardware, network services and protocols, software, and firmware. The following list identifies the top-level device properties categories and provides a short description of the types of properties within each category.

- Hardware Architecture: The processors, memory, storage, Field Programmable Gate Arrays (FPGA), and other circuit-board level components, along with physical interfaces used for normal device usages (e.g., consoles, serial, USB), or those used for debugging purposes (e.g., Joint Test Action Group [JTAG], Universal Asynchronous Receiver-Transmitter [UART]).

- **System Software**: The underlying system-level software that controls the device (e.g., operating systems and firmware), its capabilities, and procedures to update the software (e.g., over-the-air update).

- Application Software: Software platforms (e.g., hosted web servers, web-server interaction, runtime environment) and programmability features of devices that implement its role-specific services and functionality.

<sup>&</sup>lt;sup>6</sup> Cybersecurity Alerts & Advisories. URL: https://www.cisa.gov/news-events/cybersecurity-advisories

All rights reserved. Approved for public release; Distribution unlimited. Public release case number: 24-00165-1

• Networking: Device-based networking hardware (e.g., Ethernet interfaces, Bluetooth receiver/transmitters) and associated protocols supported by these interfaces (e.g., Open Platform Communications United Architecture [OPC UA], Controller Area Network [CAN bus]).

Each of these high-level categories is then further divided into sub-properties that are then mapped to a set of threats. The properties mapping informs users which threats are associated with a given device property. The properties mapping is not intended to enumerate every relevant precondition or requirement that determines the credibility of the threat, but rather to provide sufficient distinction between which threats are most relevant.

## 3.2 Threat Properties

The threats, which are mapped to the previously identified device properties, identify how a threat actor can achieve some objective or effect on a system or device. Each threat will include the following information:

- Threat ID: This is a unique identifier for the threat, expressed in the format TID-###.

- Threat Overview: This is a short description of the threat.

- **Threat Description:** This is a more complete description of the threat. The description includes (i) information about the technical mechanisms/features that are targeted by the threat; (ii) the actions that must be performed by the threat actor to cause the threat's effect, including the impact or effect the threat will have on the device; and (iii) the vulnerabilities or weaknesses within that mechanism that enable the threat actions.

- Threat Maturity and Evidence: This provides background information on the threat, including its current maturity level and evidence supporting its feasibility:

- *Threat Maturity:* This defines the maturity of the threat, including whether it is an Observed Adversarial Technique, Known Exploitable Weakness (KEV), Proof of Concept, or Theoretic threat.

- *Threat Evidence:* This provides references to the specific threat event, including ATT&CK TTPs, technical reporting, and research papers/presentations defining the threat. The exact contents of this field depend on the defined Threat Maturity level, as defined in the following table.

| Threat Maturity                | Threat Evidence                                                                                       |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------|--|--|

| Observed Adversarial Technique | ATT&CK technique or documented report                                                                 |  |  |

| Known Exploitable Weakness     | Documentation of known weakness exploitation,<br>such as a CWE associated with a KEV catalog<br>entry |  |  |

| Proof of Concept               | Reference to research paper/report                                                                    |  |  |

| Theoretic                      |                                                                                                       |  |  |

• **Supporting Weaknesses and Vulnerabilities:** This provides information about weaknesses that correlate with the threat, and specific examples of these weaknesses being observed within embedded devices.

4 ©2024 The MITRE Corporation.

- *Weakness:* The CWE best associated with this threat. This mapping is to a CWE with the lowest possible Abstraction level (e.g., Variant, Base), but will map to a higher-Abstraction level CWE (e.g., Pillar, Class) if a relevant lower-level one is not available.

- *Vulnerabilities:* Where available CVE mappings are provided as an example of that weakness being identified on an embedded device.

### 3.3 Mitigations

A set of mitigations are documented for each threat. They are primarily intended to be used by device vendors to either prevent or reduce the risk of a threat but can also be used by end users to validate that devices include recommended mitigations. Mitigations are discussed at a high level to define what mechanisms or technologies provide protection from that threat while retaining flexibility regarding how mitigations can be implemented within the unique constraints of the devices. Where possible, EMB3D<sup>TM</sup> includes information about inadequacies, weaknesses, and implementation challenges with implementing different mitigations to provide more context regarding their adoption. Additional scoping of mitigations is defined below:

- Focus on Technical Mitigation to Threats versus Architectural Protections: Mitigations focus specifically on mechanisms that protect devices against or reduce the impact of threats, as opposed to network architecture, deployment, or implementation guidance that could reduce the device's overall exposure to threats. This focus is to encourage device vendors to build in technical mitigations for threats, rather than recommend general architectural guidance that may not be either as practical or as effective in all deployments. For example, vendor guidance suggesting that either (i) the device should be isolated from other devices on a network or (ii) additional monitoring capabilities are needed to detect the threat will not be considered adequate mitigations for EMB3D<sup>TM</sup>.

- Maturity Tiers: While each threat will include mitigation guidance, these often have varying efficacies and challenges with their implementation. For example, many standards or best-practice guidelines exist stating how to update firmware securely, deploy encryption on communications, or harden systems against memory corruption attacks. However, more emerging threats typically do not have well understood mitigations. Often there are different methods that could be adopted to mitigate a threat, but implementing these may present different cost or challenges. Therefore, EMB3D<sup>TM</sup> mitigations will be mapped to one of three tiers, Foundational, Intermediate, and Leading. Foundational mitigations are the minimal capability deployed to a device with an associated threat. Foundational mitigations must have well defined implementation guidelines to ensure they can be broadly adopted by devices. Intermediate mitigations are those that have been broadly adopted by systems in other domains (e.g., IT, mobile), but may introduce additional costs which have prevented their adoption in embedded devices. Finally, Leading mitigations are those that include novel mechanisms and have not been broadly deployed. These typically lack common implementation guidance which prevents them from being deployed more broadly.

## 4 Users and Workflow

### 4.1 Workflow

The recommended workflow for applying EMB3D<sup>TM</sup> incorporates three steps: (1) enumerate device properties and map to threats, (2) enumerate threats and evaluate their relevance/risk, and (3) map to mitigations. Each of these are described in more detail below.

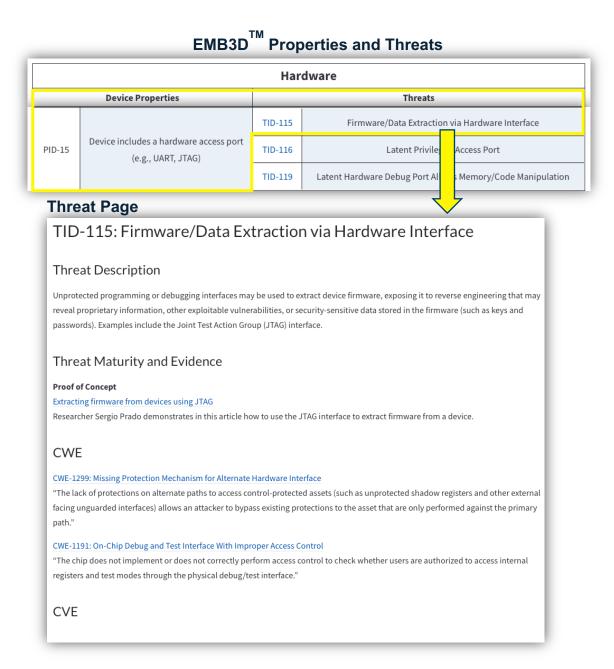

**Step 1. Enumerate device properties and map to threats:** The user first enumerates a set of relevant device properties based on any relevant information about the device. While a vendor may be able to fully enumerate all properties, an asset owner or security researcher may need to review available documentation or perform initial device testing or decomposition to fully enumerate the relevant properties. Figure 2 demonstrates the device properties and sub-properties associated with the device's firmware, and their mapping to specific threats. The yellow boxes are intended to demonstrate the identification of a device's relevant properties and their mapping to specific threats.

| Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EMB3D <sup>™</sup> Properties and Threats |                                                                                        |                               |                                                            |   |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------|---|--|

| 999999                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Hardware                                  |                                                                                        |                               |                                                            |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Device Properties                         |                                                                                        |                               | Threats                                                    | l |  |

| 66666                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PID-11                                    | Device includes a microprocessor                                                       | TID-101                       | Power Consumption Analysis Side Channel                    | l |  |

| Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           |                                                                                        | TID-102                       | Electromagnetic Analysis Side Channel                      | l |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                                                                                        | TID-103                       | Cache Timing Analysis Side Channel                         | l |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                                                                                        | TID-105                       | Hardware Fault Injection – Control Flow Modification       | l |  |

| Hands-on Examination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PID-121                                   | Device includes buses for external<br>memory/storage                                   | TID-106                       | Data Bus Interception                                      |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PID-122                                   | Device includes discrete chips/devices that<br>have access to the same physical memory | TID-107                       | Unauthorized Direct Memory Access (DMA)                    |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PID-123                                   | Device includes ROM, VRAM, or removable<br>Storage                                     | TID-108                       | ROM/NVRAM Data Extraction or Modification                  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PID-124                                   | Device includes Random Access Memory<br>(RAM) chips                                    | TID-109                       | RAM Chip Contents Readout                                  |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PID-1241                                  | Device includes DDR DRAM                                                               | TID-110                       | Hardware Fault Injection - Data Manipulation               | l |  |

| and the second sec | PID-13                                    | Device includes peripheral chips and                                                   | TID-113                       | Unverified Peripheral Firmware Loaded                      | l |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10-13                                     | integrated data buses                                                                  | TID-114                       | Peripheral Data Bus Interception                           | l |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PID-14                                    | Device includes external peripheral<br>interconnects (e.g., USB, Serial)               | TID-111                       | Untrusted External Storage                                 | l |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                                                                                        | TID-118                       | Weak Peripheral Port Electrical Damage Protection          | l |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PID-15<br>(e.g., UART, JTAG)              |                                                                                        | TID-115                       | Firmware/Data Extraction via Hardware Interface            | l |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           | TID-116                                                                                | Latent Privileged Access Port | l                                                          |   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                                                                                        | TID-119                       | Latent Hardware Debug Port Allows Memory/Code Manipulation |   |  |

### EMB3D<sup>™</sup> Properties and Threats

Figure 2. Enumerating Device Properties Using EMB3D<sup>™</sup>

6

**Step 2. Enumerate threats and evaluate their relevance/risk:** After the user has defined a set of device properties, they should review each threat mapped to those properties (Figure 3). The threat description provides additional information about the threats, including the maturity level and documented threat evidence. Using this information, the user can better understand the risk of that threat and determine whether additional mitigations are warranted. Further, references to relevant CVEs and CWEs provide the user with information about a device's specific weaknesses that enable the threat.

#### Figure 3. Mapping Device Properties to Threats and Associated Weakness and Vulnerability Information

7 ©2024 The MITRE Corporation.

**Step 3. Map to mitigations:** If a threat is considered a viable risk to the device, the associated mitigations provide guidance on what technical mechanisms can best prevent or reduce the risk of that threat. The mitigations will include references to guidance documents and best practices, along with information about potential limitations/challenges when deploying each mitigation.

# 4.2 EMB3D<sup>™</sup> Use Cases for Vendors, Asset Owners, Security Researchers, and Testing Organizations

EMB3D<sup>TM</sup> was developed to support distinct roles and organizations within the security community, specifically (i) vendors product development teams, (ii) asset owner security architects, and (iii) security researchers/testing organizations. Because each of these roles may have slightly different use cases, this section highlights how EMB3D<sup>TM</sup> can be used to support each role.

### 4.2.1 User 1: Vendor Product Team

The design and development of a device requires numerous decisions regarding the cost, reliability, and consumer demand of various features and capabilities. EMB3D<sup>TM</sup> can be used by product security teams to better communicate to product development teams the need for certain product security investments by providing a consistent and standardized view about what threats exist and what mechanisms are needed to address them. By comparing device properties and currently implemented security mechanisms, EMB3D<sup>TM</sup> enables security and product teams to efficiently identify the strengths and potential weaknesses in a device's security posture. It can then help product managers, architects, and security teams work together to prioritize security-focused development to obtain more robust mitigation coverage against the most likely threats. Further, the model's mitigations content helps guide developers towards implementing more effective defenses and avoiding common pitfalls, altogether leading to better, more secure products.

### 4.2.2 User 2: Asset Owner Security Architect

Asset owners often struggle to assess the risks associated with using a device and are thereby challenged to specify the expected device security capabilities during an acquisition. When a device lacks adequate security, the asset owner inherits the responsibility of understanding the resulting risk and designing compensating controls into their broader architecture. It is also a challenge for an asset owner to identify what security testing should be performed on the device to ensure security capabilities have been completely and correctly implemented.

Asset owners can leverage EMB3D<sup>TM</sup> to hold vendors more accountable for risk by requiring (i) detailed mappings of device properties, and (ii) documentation of the mitigations that have been built into the device to address the threats associated with those device properties. Requirements for vendors to provide this device data can be included in procurement language to ensure asset owners can more directly evaluate threats associated with those properties. Further, asset owners can use EMB3D<sup>TM</sup> to scope security testing efforts to better assess device risks and protections. EMB3D<sup>TM</sup> provides a common language and framework for asset owners to communicate to vendors regarding device security requirements, what threats need to be addressed, and the necessary mitigations for those threats.

8

### 4.2.3 User 3: Security Researcher/Testing Organization

Security researchers and testing organizations can use EMB3D<sup>TM</sup> to develop a more standard framework and methodology to assess devices based on a common language to describe device properties, threats, and mitigations. The framework can aid in the development of test plans to help provide clear guidelines on what threats and mitigation testing activities will focus on, and which are out of scope for a specific effort. Further, by mapping test outcomes or findings to EMB3D<sup>TM</sup> threats, a finding's severity and credibility can be more clearly communicated.

## 5 Conclusion

This paper introduces the EMB3D<sup>TM</sup> threat model for critical infrastructure embedded devices. The threat model provides a cultivated knowledge base of known cyber threats to devices, including those observed in the wild and demonstrated through proof-of-concept and theoretic research. The threats are mapped to device properties to help users develop and tailor accurate threat models for specific embedded devices. Each threat is also associated with a set of mitigations that should be adopted to reduce the risk of these threats to a device. EMB3D<sup>TM</sup> is intended to provide a common language that can be adopted by device vendors, asset owners, security researchers, and testing organizations to (i) consistently assess, understand, and prioritize threats to devices; (ii) scope device assessments and testing activities; and (iii) communicate findings and associated risks.

# Appendix A Terminology, Challenges, Scope, and Related Efforts

This appendix provides additional information on the scope and methodology associated with building the EMB3D<sup>TM</sup> threat model as well as documenting some of the challenges associated with its development.

## A.1 Terminology

While terms such as threat, threat model, weakness, and vulnerability are used heavily within the cybersecurity field, they often have imprecise or conflicting definitions. This section will define how these terms are used within EMB3D<sup>TM</sup>.

- Threats: An action or set of actions that a threat actor may use to achieve some objective or effect on a system or device.

- **Threat Model:** A set of threats that have been identified to be relevant to a specific system or device.

- Weakness: "A condition in a software, firmware, hardware, or service component that, under certain circumstances, could contribute to the introduction of vulnerabilities."<sup>7</sup>

- Vulnerability: "A flaw in a software, firmware, hardware, or service component resulting from a weakness that can be exploited, causing a negative impact to the confidentiality, integrity, or availability of an impacted component or components."<sup>8</sup>

Threats are closely related to weaknesses and vulnerabilities in that weaknesses/vulnerabilities do not present any risk in the absence of a threat. While threats describe the actions necessary for the actor to achieve an effect on a device, weaknesses and vulnerabilities define the technical limitations and means that enable that threat behavior. While weakness enumerations (e.g., CWE) provide significant value to the identification and mitigation of weaknesses in systems, understanding whether and how a threat can potentially target a weakness is important to understanding that weaknesses, such as CWEs, there are also numerous examples where threat actors target normal system functions to achieve their objective, including mechanisms to discover devices<sup>9</sup> or to leverage existing services to gain access.<sup>10</sup> While these threats may not always have practical or effective mitigations, understanding how a threat actor may target and interact with a device is still an important factor in the overall understanding and assessment of risks.

©2024 The MITRE Corporation.

<sup>&</sup>lt;sup>7</sup> CWE Glossary. URL: https://cwe.mitre.org/documents/glossary/index.html

<sup>&</sup>lt;sup>8</sup> CWE Glossary. URL: https://cwe.mitre.org/documents/glossary/index.html

<sup>&</sup>lt;sup>9</sup> Remote System Information Discovery. MITRE ATT&CK. URL: https://attack.mitre.org/techniques/T0888/

<sup>&</sup>lt;sup>10</sup> Remote Services. MITRE ATT&CK. URL: https://attack.mitre.org/techniques/T0886/

All rights reserved. Approved for public release; Distribution unlimited. Public release case number: 24-00165-1

## A.2 Threat Maturity

Understanding the credibility and maturity of a threat is critical to determining whether it should be included in a threat model. While knowledge bases such as ATT&CK document observed adversarial techniques, many other threats have been observed only in laboratory/testbed environments or have only theoretic explanations. Due to the long lifespan of embedded devices and the shifting threat landscape, devices must be designed to be secure against both currently observed and expected future threats. To help distinguish the creditability of a threat, each is assigned one of four categories: (i) Observed Adversarial Technique, (ii) Known Exploitable Weakness, (iii) Proof of Concept, and (iv) Theoretic. Each category is defined in more detail below.

**Observed Adversarial Technique:** This type of threat has been observed in use by cyber adversaries to target embedded devices or critical infrastructure environments. This requires a reference to observed adversarial use of the threat, such as an ATT&CK Procedure Example, or reference to a reputable CTI report documenting the observed use. It can also include information about the vulnerabilities in devices (e.g., CVEs) or general categories of vulnerabilities (e.g., CWEs).

**Known Exploitable Weakness:** This includes well-defined weaknesses, specifically those defined by CWEs, that have been demonstrated to be exploitable by threat actors in other nonembedded environments (e.g., Enterprise, Mobile). This category is used to ensure threats that have been broadly observed targeting weaknesses within other environments are equally prioritized. Meeting this maturity level assumes the threat is known to target a technology-specific CWE (either at the Base or Variant abstraction), and that there is evidence that CWE has shown to be exploitable. One potential example for evidence of exploitation is a mapping to a CVE that is known to be exploited by its inclusion within the DHS Known Exploited Vulnerabilities (KEV) Catalog.<sup>11</sup>

**Proof of Concept:** A proof-of-concept threat requires evidence that it has been demonstrated under sufficiently realistic assumptions to validate its effectiveness. For a threat to be considered a viable proof of concept, it requires the following:

- 1. Demonstration that the threat can have its intended effect/impact on a realistic target (e.g., software, device, network),

- 2. Demonstration that the information required for the threat's execution can be obtained,

- 3. Demonstration that necessary environmental assumptions, human interactions, or corresponding events are reasonable,

- 4. Availability of defensible materials to further prove the concept (e.g., video recording, Github publishing, full documentation of the work completed and its effects).

**Theoretic:** This type of threat has not yet been sufficiently demonstrated to verify its effectiveness against real-world environments. The threat may be dependent on insufficiently validated assumptions regarding the reliability of a technical exploitation mechanism, or a threat

<sup>&</sup>lt;sup>11</sup> Known Exploited Vulnerabilities Catalog. CISA. URL: https://www.cisa.gov/known-exploited-vulnerabilities-catalog

All rights reserved. Approved for public release; Distribution unlimited. Public release case number: 24-00165-1

actor's computing resources, level of access, information, or operational capabilities. Strong supporting reference material, such as peer-reviewed research reports documenting the threat activity, is necessary to address factors such as those listed above and to contextualize it in relation to other vulnerability and weakness categories. Examples include:

- Threats with ambiguous/hypothetical computing resources. An example could be assumptions that the threat actor has a functional quantum computer and therefore can break asymmetric encryption keys.<sup>12</sup>

- Threats with unclear assumptions about the required adversarial access, information, or algorithmic complexity necessary for execution. For example, there is a wide number of academic efforts discussing False Data Injection Attacks on theoretic controls or sensor models<sup>13</sup> that lack demonstration on real networks/software platforms.

- Threats lacking demonstrated/reliable exploitation mechanisms. These threats could include exploits that inconsistently work but have been proved to be feasible under specifically scoped environments/testing set-ups.

## A.3 Key Challenges

Developing a threat model that is broadly useable for a wide-ranging set of organizations including device vendors, security researchers/testing organizations, and integrators/asset owners—presents multiple challenges, including:

- Identifying Relevant Threats: Information about threats to devices can be found across a diverse set of sources. Existing knowledge bases such as MITRE ATT&CK<sup>14</sup> include information about known adversary behavior, while platforms such as CVE, CISA ICS Advisories,<sup>15</sup> and CWE define weaknesses and vulnerabilities within hardware and software platforms. Additionally, there exists a wide range of theoretic and proof-of-concept vulnerability research efforts that have been demonstrated by security researchers and are documented through various security conferences, papers, blogs, and other sources.

- Understanding the Evolving Threat Landscape: Threats continually evolve, both in the set of techniques they utilize and in the environments they target. Security researchers are continually identifying new methods by which systems can be manipulated. These often begin as theoretical ideas, which often lead to proof-of-concept demonstrations, and then may eventually be adopted and used by threat actors. Further, threat techniques that are identified in certain sectors or devices, such as traditional IT environments, may be adopted and tailored to critical infrastructure sectors. Therefore, the model must include

#### ©2024 The MITRE Corporation.

<sup>&</sup>lt;sup>12</sup> Ford, Pete. "The quantum cybersecurity threat may arrive sooner than you think." Computer 56.2 (2023): 134-136.

<sup>&</sup>lt;sup>13</sup> Mo, Yilin, and Bruno Sinopoli. "False data injection attacks in control systems." Preprints of the 1st workshop on Secure Control Systems. Vol. 1. 2010.

<sup>14</sup> MITRE ATT&CK: URL: https://attack.mitre.org

<sup>&</sup>lt;sup>15</sup> Cybersecurity Alerts & Advisories. URL: https://www.cisa.gov/news-events/cybersecurity-advisories

threats of varying maturity levels and across the diverse sectors where the threats have been observed.

- Scoping/Prioritizing Threats: There is a range of potential threats a device could be vulnerable to, ranging from those in active use by threat actors to theoretic threats that are currently not technically possible. Further, threats are typically aligned to specific technical properties or architectures, which may have varying prevalence across embedded devices. Therefore, the threat model must bound the included threats based on the (i) credibility of the threat, (ii) technologies/architectures for which threats are identified, and (iii) level of detail regarding the threat such that it is sufficiently applicable to a broad set of embedded devices.

- Identifying Commonalities with Embedded Devices and Properties: Devices used across the critical infrastructure embedded technology domain are very diverse. The threat model must scope and abstract the large set of technologies and device features down to a manageable number of unique properties. In many cases, this will also require abstracting threats—for example, identifying and combining general threats to network protocols in general, rather than defining individual threats to the large set of specific protocols or implementations.

- Identifying Mitigations and Countermeasures: Where practical, the threat model identifies mitigations and countermeasures against enumerated threats. The mitigations and countermeasures proposed in the model are not intended to be used as a definitive security checklist or one-size-fits-all approach, as devices with unique architectures, implementations, and constraints may necessitate customized mitigations and countermeasures. Additionally, not all mitigations are equally effective and may leave residual risks that still constitute a threat to the device. For example, encrypting/authenticating network traffic will mitigate certain threats, but introduce additional threats associated with known weaknesses in cryptographic mechanisms.

## A.4 Scoping

Threat scoping is provided below and is intended to inform users on where EMB3D<sup>™</sup> should be used, what is included in the threat model, and what is specifically excluded. Key elements of scope are enumerated below:

- No Network Architecture or Sector Operational Properties: The threats within EMB3D<sup>TM</sup> are mapped to specific properties and features of a specific device. They do not include any context or reference to the device's position within a specific network architecture or its specific operational functions within an organization. This is because devices are often used across a diverse set of architectures or operational roles, which inhibits the development of a complete and accurate enumeration of these uses for a device.

- Focused on Atomic Threat Techniques Rather than Exploit Chaining: The threats within the model are scoped to events that are used to bypass the confidentiality, integrity, or availability of some property of a device. EMB3D<sup>TM</sup> does not explicitly model threats that consist of a sequence of events that must be chained together to achieve a specific effect on a device. For example, a threat actor may be able to reverse

13

©2024 The MITRE Corporation.

engineer a device to gain a valid authentication key and then use that key to remotely access a device. Within EMB3D<sup>TM</sup>, this scenario would be categorized as two discrete threats.

- Access to Devices: The threat actor is considered to have physical access to instances of the device that can be used to conduct vulnerability research and exploit development prior to execution of an attack, including performing reconnaissance and reverse engineering.

- **Relevance to Embedded Devices:** The threat model is focused on embedded devices; therefore, the properties and features have been scoped to these devices. Embedded devices include a broad set of unique technologies used within embedded applications, along with dependencies on more diverse technologies used across general computing platforms/environments. Therefore, the scope will include both categories, as defined in the following table.

|          | Properties of Defined Technologies and Platforms                                                                                                                                                                                                                       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|